Page 21 - Telebrasil - Setembro/Outubro 1978

P. 21

pendente. Entretanto esta última

forma náo é a mais econômica,

pois este equipamento duplicaria

muitas das funções do terminal INSCREVER - 8 4 KHZ I EQUIR TERMINAL PCM

PCM. poio» rJ...,,.]. , [.1.l.„rJ..l...l f J.

OR KC. M M l M 2 M 3 M 4 M 3 MS M 7 | M

Partindo da filosofia de incorporar

Linho

a unidade de acesso ao terminal LEITURA"— ' 0 4 9 1<HÍ XõãTkoí“

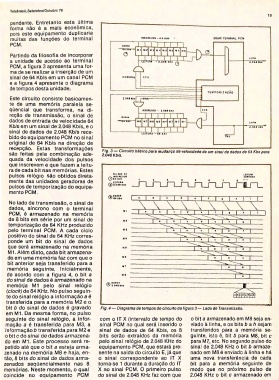

PCM, a figura 3 apresenta uma for

ma de se realizar a inserção de um

sinal de 64 Kb/s em um canal PCM 2.048 KHz I T. X.

e a figura 4 apresenta o diagrama

de tempos desta unidade,

T E M P O R I Z AÇÁO

v '

Este circuito consiste basicamen 2 04 8 KHZ

te de uma memória paralela se-

qüencial que transforma, na di INSCREVER - 2.048 KHZ I T X.

reção de transmissão, o sinal de 00009 L I ¦ X I .

H

dados de entrada de velocidade 64 T U T j M a | M r j M* H 4 | M 3 | M 2 | Linho

;

M

Kb/s em um sinal de 2.048 Kb/s, e o 2 . 0 4 $ KOI

sinal de dados de 2.048 Kb/s rece EXT TL

LEITURA - 64 KHl

bido do equipamento PCM no sinal

original de 64 Kb/s na direção de

recepção. Estas transformações

Fig. 3 — Circuito básico pera mudança de velocidade de um sinal de dados de 64 Kbs para

são feitas pela combinação ade 2.048 Kb/s.

quada da velocidade dos pulsos

que inscrevem e que fazem a leitu

ra de cada bit nas memórias. Estes

pulsos relógio são obtidos direta PULSOS Pé LCiruRA

INSCPCVÍT

2044KHl

© 04 KHl

mente das unidades geradoras de

LCITUPA ! I ÜJ

pulsos de temporização do equipa ( a ) 3.044 KNt

mento PCM.

No lado de transmissão, o sinal de

dados, síncrono com o terminal

PCM, é armazenado na memória

de 8 bits em série por um sinal de

temporização de 64 KHz produzido

pelo terminal PCM. A cada ciclo

positivo do sinal de 64 KHz corres

ponde um bit do sinal de dados

que será armazenado na memória

M1. Além disto, cada bit armazena

do em uma memória faz com que o

bit anterior seja transferido para a

memória seguinte. Inicialmente,

de acordo com a figura 4, o bit a

do sinal de dados é armazenado na

memórja M1 pelo sinal relógio

(clock) de 64 KHz. No pulso seguin

te do sinal relógio a informação a é

transferida para a memória M2 e o

bit b do sinal de dados é gravado Fig. 4 — Diagrama de tempos do circuito da figura 3 — Lado de Transmissão.

em M1. Da mesma forma, no pulso

seguinte do sinal relógio, a infor com o IT X (intervalo de tempo do o bit a armazenado em M8 seja en

mação a é transferida para M3, a sinal PCM no qual será inserido o viado à linha, e os bits b ah sejam

informação b transferida para M2 e sinal de dados de 64 Kb/s, os 8 transferidos para a memória se

o bit c do sinal de dados armazena bits serão extraídos da memória guinte, isto é, bit b para M8, bit c

do em M1. Este processo será re pelo sinal relógio de 2.048 KHz do para M7, etc. No segundo pulso do

petido até que o bit a esteja arma equipamento PCM, que estará pre sinal de 2.048 KHz o bit b armaze

zenado na memória M8 e haja, en sente na saída do circuito E, já que nado em M8 é enviado à linha e há

tão, 8 bits do sinal de dados arma o sinal correspondente ao IT X uma nova transferência de cada

zenados seqüencialmente nas 8 torna-se 1 durante a duração do IT bit para a memória seguinte de

memórias. Neste momento, o qual X no sinal PCM. O primeiro pulso modo que no próximo pulso de

coincide no equipamento PCM do sinal de 2.048 KHz faz com que 2.048 KHz o bit c armazenado em